Big things sometimes come in small packages. Version 1.2.0 of the award-winning SERV, the

world's smallest RISC-V CPU has been released and it's filled to the brim with new features.

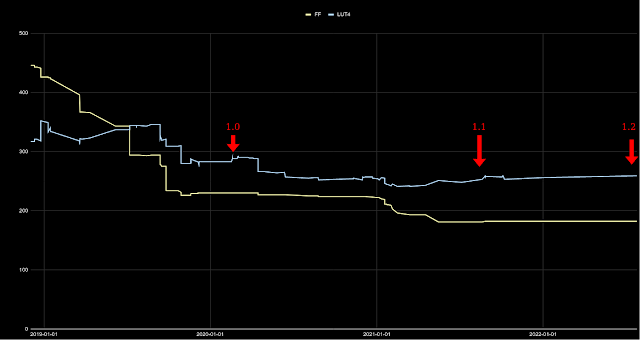

Historically, focus has always been on size reduction, making it ever smaller, and that has paid off. It's now about half the size of when it was first introduced. But at this point we're not really getting much smaller, and frankly, that's fine. It still is the world's smallest RISC-V CPU by a good margin.

|

| Resource usage over time for the SERV default configuration |

|

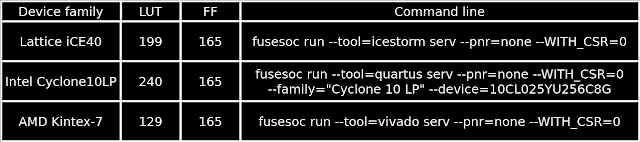

| Mimimum SERV resource usage for some popular FPGA families |

So this time we focus on features instead. Most notably we have support for two major ISA

extensions, both often requested by users, but there are also a number of other new

features as well. Let's take a look at all of them, shall we?

M extension

|

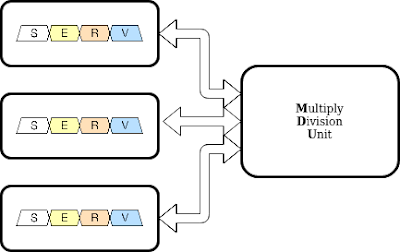

| Multiple SERV cores can share one MDU (or perhaps other accelerators) |

As

part of Google Summer of Code 2021, Zeeshan Rafique implemented support

for the M ISA extension. This was done through an extension interface

that allows the MDU (Multiplication and Division Unit) to reside outside

of the core and potentially be shared by several SERV cores in the same

SoC, or integrated into other RISC-V cores for maximum reusability.

We hope to also see other accelerators use the extension interface soon. Zeeshan's report about the project to add the M extension can be read

here

C extension

|

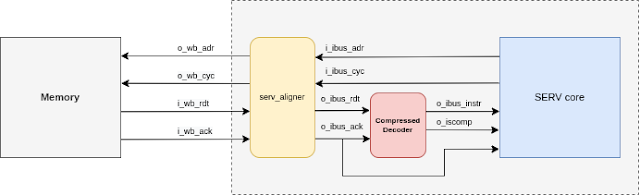

| Two extra blocks to save a lot of memory |

As part of the Linux Foundation Mentorship

program Spring 2022, Abdul Wadood has implemented support for the C ISA

extension. The C extension has been the most requested feature of SERV.

Since SERV is so small, the memory typically dominates the area and the C

extension has the potential to allow for smaller memories and by

extension a smaller system. Abdul's report about the project to add the C

extension can be read here

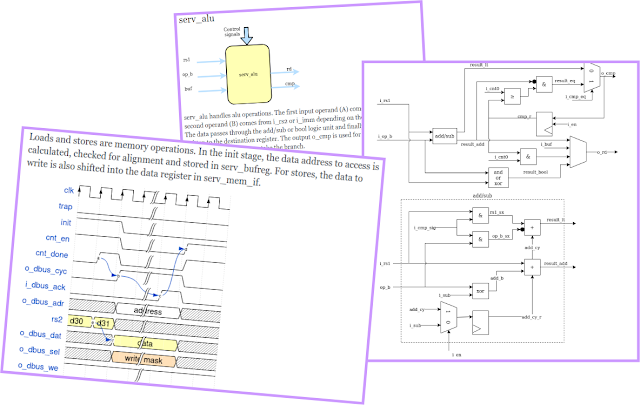

Documentation

|

| Pictures and words. The SERV documentation has it all |

Documentation

continue to improve with more gate-level schematics, written

documentation, source code comments and timing diagrams towards the goal

of becoming the best documented RISC-V CPU. There are always room for improvements, but now all modules as well as the external interfaces are at least documented.

Bug fixes

A bug

that caused immediates to occasionally get the wrong sign (depending on

which instruction was executed prior to the failing one) was found and

fixed.

Model/QuestaSim compatibility has been restored after accidentally being broken after the 1.1.0 release and a few more resets have been added after doing extensive x-propagation analyses.

Compliance tests

Version

2.7.4 of the RISC-V compliance test suite is now supported over the

older 1.0 release. A Github CI action has also been created to test the

compliance test suites with all valid combinations of ISA extensions for

improved test coverage.

Servant

Moving outside of the SERV core itself we have Servant, the simple SERV reference SoC. Servant isn't the most feature rich SoC, instead focusing on simplicity, but it has at least the bare minimum to run the popular Zephyr Real Time Operating System. During this development cycle Servant, has gained support for five new FPGA boards: (EBAZ4205, Chameleion96, Nexys2 500, Nexys2 1200 and Alinx AX309)

With this, the total number of officially supported boards is 26.

ViDBo support

|

| Got no FPGA board? Don't worry. ViDBo has you covered. |

Support for the

Virtual Development Board protocol has been added, making it possible to

interact with a simulation of an FPGA board running a SERV SoC, just as

it would be a real board. This allows anyone to build software for SERV

and try it in simulation without access to a real board.

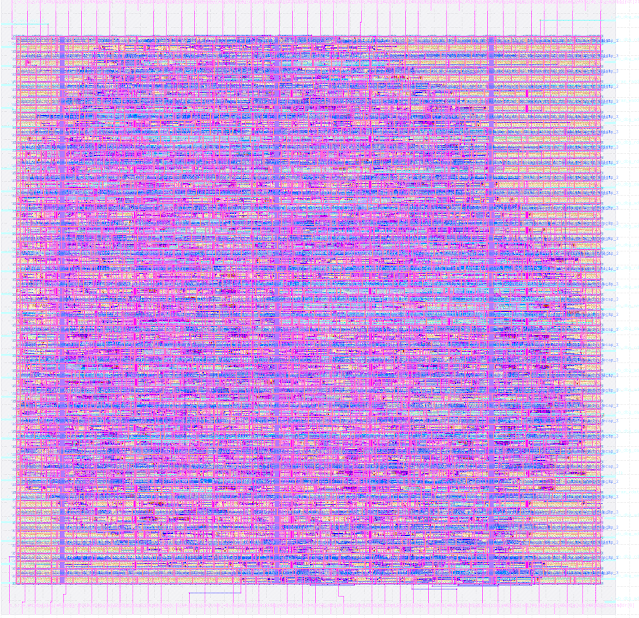

OpenLANE support

|

| A few thousand transistors needed to build the world's smallest RISC-V CPU |

Thanks

to the FOSSi OpenLANE toolchain, SERV can be implemented as an ASIC

with the SkyWater 130nm library. It has also been taped out as part of the

Subservient SoC but at the time of this release the chips have not yet

returned from the fab. Thanks to the combination of a FuseSoC, a FOSSi

ASIC toolchain and publicly available CI resources however, a GDS file

of SERV is now created on every commit to the repository, making the

ASIC process about as agile as it can get.

The future

So what lie as ahead for

our favorite CPU? Well, there were a number of features that I decided

to postpone in order to get a new version released. There were plenty of

big features anyway

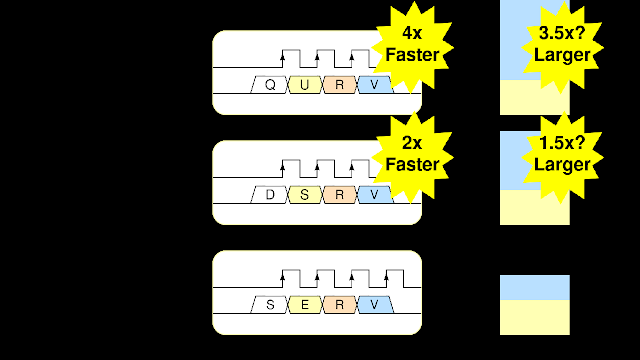

DSRV & QERV

|

| Smaller or faster. The choice is yours. |

SERV is very small.

That's kind of the point. However, many times it's preferable to use

slightly more resources if it also means faster. Changing to a 2-bit

datapath would make SERV twice as fast, while likely using far less than

twice as much logic. Moving to a 4-bit datapath would halve the CPI

once again. The 2- and 4-bit versions are tentatively called DSRV, for

Double SERV, and QERV, for Quad SERV. I think you get the point, but here's a video explaining the

idea in slightly more detail if anyone is interested in taking up this

as a project.

While we could theoretically go for 8-, 16- and

32-bit versions as well, there are some internal design choices that

would make this more complicated and it would probably be a better idea

to design a new implementation from scratch for 8+ bit datapaths.

Decoder generator

Another big thing that I had hoped to finish but decided to push to a future version is autogenerated decoder modules. I have spent a lot of work on it and I think it's a really interesting idea that might even end up as a paper at some point. Unfortunately I don't have the time to finish it up right now. So, what's it all about? Well, it's a bit complicated so I think it's best to leave the details to a separate article (which I hope to find time to write soon), but the overall idea is to take advantage of the fact that many internal control signals are irrelevant when executing some class of instructions, so that we can combine them with other control signals that are irrelevant for other classes of instructions.

Servant

I was also hoping to add some improvements to Servant, the SERV reference platform but couldn't find time for that either. I think that's ok though. Anyone who's looking for a more advanced platform to run SERV should go for Litex instead which supports SERV already. Fellow RISC-V ambassador Bruno Levy even demonstrated that it was possible to run DooM on SERV through Litex, I might be a bit partial, but it's a beautiful thing to see this tiny thing take on such a big task and as a proud parent I look at it and wonder is there anything this little CPU can't do with a little encouragement.

No comments:

Post a Comment